文章编号: 1671-251X(2010)07-0131-04

# 一种 DSP 对地址数据总线复用器件的驱动方法

邵勇<sup>1</sup>, 张国强<sup>2</sup>, 康安明<sup>3</sup>

(1. 煤炭科学研究院常州自动化研究院, 江苏常州 213015; 2. 枣庄矿业集团柴里煤矿, 山东枣庄 277519; 3. 江苏科技大学计算机科学与工程学院, 江苏镇江 212003)

**摘要:** 针对工业控制开发领域存在的器件总线结构不兼容问题, 提出了一种采用 CPLD 实现的 DSP 驱动地址数据总线复用器件的方法, 并以 TMS320LF2407A DSP 访问 DS12C887 时钟芯片为例讲述了具体实现过程, 并给出了在设计过程中应注意的速度匹配、信号电平匹配、信号格式匹配和时序匹配等问题。实践证明, 该方法简便可靠, 是一种解决两种总线器件互联的可行方案。

**关键词:** 地址总线; 数据总线; 分时复用; DSP; CPLD; 驱动

中图分类号: TD679

文献标识码: B

## 0 引言

现今流行的通用工业控制 CPU 主要有单片机、ARM 和 DSP 等。随着这些控制芯片的广泛应用, 与之配套的外围芯片也是层出不穷, 随着芯片生产工艺与技术的进步, 不仅芯片功耗降了又降, 而且端口电平也有 5 V、3.3 V、1.8 V 等多种电压等级, 为工业控制产品开发尤其是终端设备控制器的开发提供了更多选择, 同时也带来了一些器件不兼容的问题。常见的不兼容问题主要表现在总线结构不兼

容、电压等级不兼容、数据格式不兼容、芯片速度不匹配及时序不匹配等方面, 其中又以总线结构不兼容最难解决。由于单片机采用普林斯顿存储结构, 地址总线与数据总线复用, 而 DSP 采用哈佛结构, 地址总线与数据总线是分开的, 这就出现了一个新的问题, 那就是如何才能将在 2 种不同总线模式下工作的芯片更好地应用在一个系统中, 使它们能够协调有序地工作在一起。本文以 TMS320LF2407A DSP 驱动 DS12C887 时钟芯片为例, 介绍了一种基于 CPLD 的总线控制方法, 从而解决这个问题。

## 1 2 种总线及相关芯片的介绍

普林斯顿结构是一种将程序指令存储器和数据存储器合并在统一编址的存储器结构。程序指

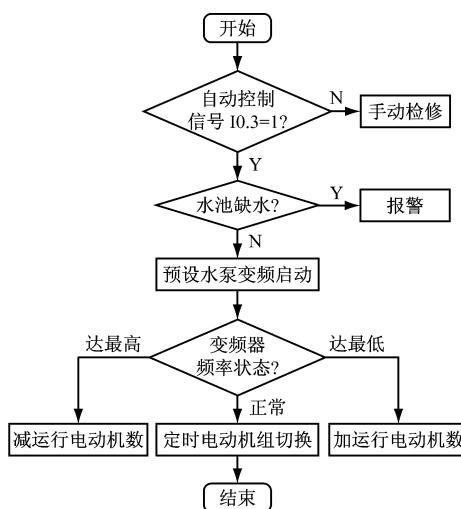

图 5 PLC 程序流程

## 参考文献:

- [1] 李勇伟. 基于 PLC 的新型变频调速恒压供水系统 [M]. 北京: 机械工业出版社, 2004.

- [2] 周万珍, 高鸿斌. PLC 分析与设计应用 [M]. 北京: 电子工业出版社, 2004.

- [3] 戴仙金. 西门子 S7-200 系列 PLC 应用与开发 [M]. 北京: 中国水利水电出版社, 2007.

- [4] 贺玲芳. 基于 PLC 控制的全自动变频恒压供水系统 [J]. 西安科技大学学报, 2000, 20(3): 243-245.

- [5] 李道霖. 电气控制与 PLC 原理及应用 (西门子系列) [M]. 北京: 电子工业出版社, 2004.

- [6] 韩焱青. PLC 控制变频调速恒压供水系统 [J]. 武汉化工学院学报, 2000(4): 71-73.

- [7] 陆海东, 张凯. 变频调速在恒压供水系统中的应用 [J]. 科技资讯, 2007(1): 42-43.

令存储地址和数据存储地址指向同一个存储器的不同物理位置,因此,程序指令和数据的宽度相同,如英特尔公司生产的 8086 中央处理器的程序指令和数据都是 16 位宽。ARM 公司生产的 ARM7、MIPS 公司的 MIPS 处理器也采用了普林斯顿结构。在早期硬件开发成本较高时,普林斯顿结构得到了广泛应用,采用该结构的产品也具有产品应用技术成熟、使用范围广的特点。

哈佛结构是一种将程序指令存储和数据存储分开编址的存储器结构。中央处理器首先到程序指令存储器中读取程序指令内容,解码后得到数据地址,再到相应的数据存储器中读取数据,并进行下一步的操作。程序指令和数据存储分开可以使指令和数据有不同的数据宽度。另外,哈佛结构是一种程序和数据空间独立的体系结构,可以减轻程序运行时的访存瓶颈。采用哈佛结构的微处理器通常具有较高的执行效率,其程序指令和数据指令分开组织和存储,执行时可以预先读取下一条指令,实现流水重叠。该结构在 DSP、ARM9、ARM10 和 ARM11 等处理器中广泛应用,尤其是在近几年硬件开发成本迅猛降低的时期,基于该结构的处理器种类更是快速增长。

在现今的控制系统设计中,极有可能在一个项目中同时用到基于 2 种不同总线模式的处理器或外围器件。下面就以基于普林斯顿结构的 DS12C887 时钟芯片与基于哈佛结构的 TMS320LF2407A DSP 为例,讲述一种实现二者兼容的方法。

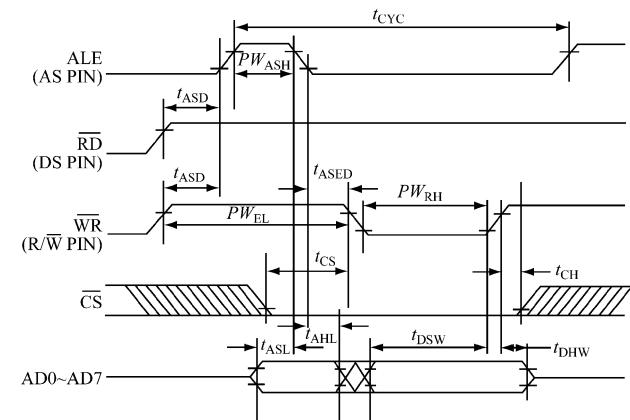

DS12C887 是美国 DALLAS 公司推出的一款内置有电池、晶振、保护电路等的时钟芯片。该芯片在系统掉电后仍能正常工作 10 年以上,其接口为 5 V 的 TTL 电平,地址与数据总线分时复用,可不需任何外加电路直接与 51 系列单片机连接,广泛应用于需要实时时钟的智能设备中<sup>[1]</sup>。该芯片在 INTEL 模式下的读写时序分别如图 1、图 2 所示。

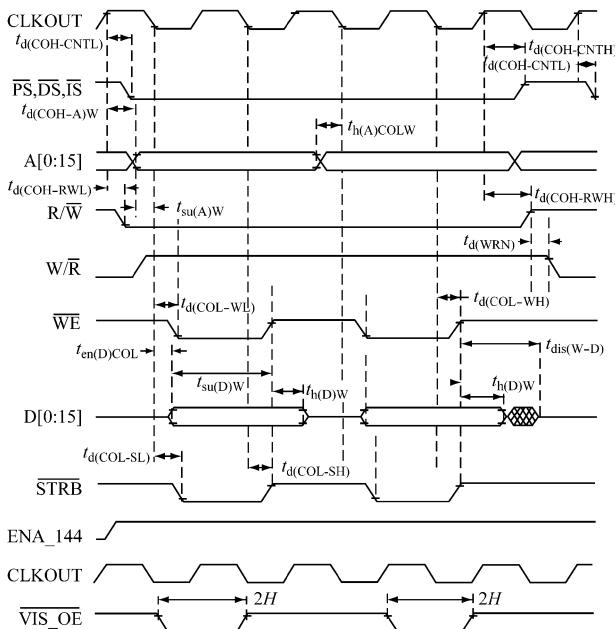

TMS320LF2407A DSP 芯片是美国 TI 公司于 20 世纪末研发的一款专门针对电动机伺服控制系统设计的专用处理器。该芯片采用 3.3 V 电源供电,具有 40 MHz 的主频、2 个事件管理器、16 路 10 位 AD、41 个可单独编程或复用的通用输入/输出口等,适用于需要对大量数据进行复杂处理的控制类产品设计,尤其是其内部的 4 级流水线设计,乘法器、加法器及反序器,是进行多点快速傅里叶变换与有限长数字滤波的较好选择<sup>[2]</sup>。该芯片接口电平为 3.3 V 的 LVTTL 电平,其对片外存储单元(此处将 DS12C887

$t_{PW_{ASH}}$  – ALE 信号有效脉冲宽度;  $t_{PW_{EL}}$  – RD 信号无效脉冲宽度;

$t_{PW_{RH}}$  – WR 信号有效脉冲宽度;  $t_{ASD}$  – 地址选通延迟时间;

$t_{CYC}$  – 周期时间;  $t_{ASED}$  – 写使能延迟时间;  $t_{CS}$  – 片选时间;

$t_{CH}$  – 片选维持时间;  $t_{DHW}$  – 写数据维持时间;

$t_{AHl}$  – 地址必要时间;  $t_{DSW}$  – 数据建立时间

图 1 DS12C887 在 INTEL 模式下的写时序

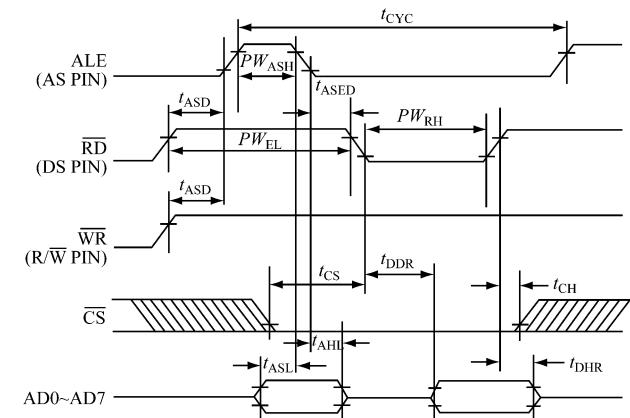

$t_{DHR}$  – 读数据维持时间;  $t_{DDR}$  – 数据输出延迟时间

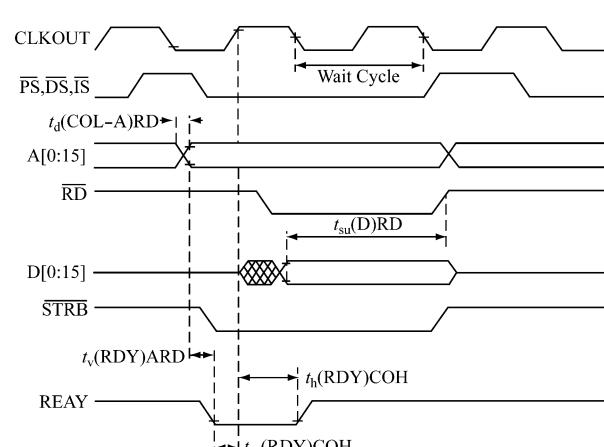

配置为外部存储器) 的读写时序分别如图 3、图 4 所示,其中,  $H$  为系统周期时间。

由上述 2 种芯片的相关介绍及读写时序可见,这 2 种芯片若共存于一个系统中,则需要解决接口方面的诸多问题。

## 2 2 种不同总线设备接口的实现方法

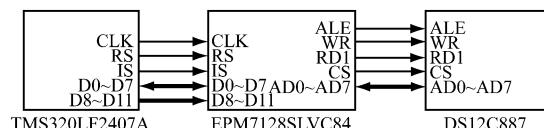

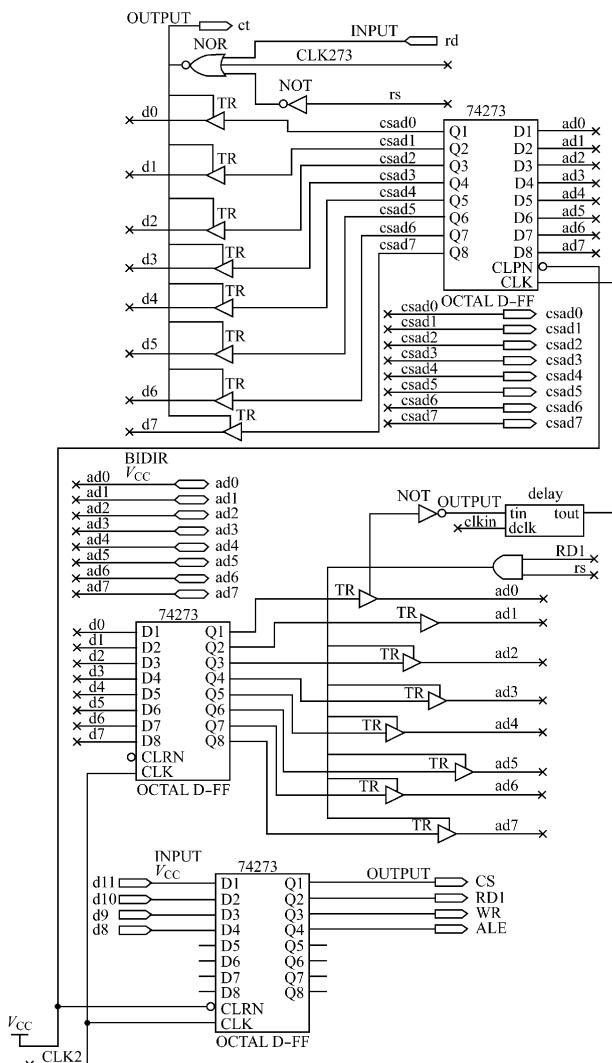

鉴于以上 2 种总线设备的区别,采用 EPM7128SLV84 CPLD 进行接口转换,以解决 2 种芯片连接时的时序问题及电平不匹配问题<sup>[3~4]</sup>。将 DS12C887 的控制线 CS、RD、WR、ALE 经过锁存器分别接在 TMS320LF2407A 数据总线 D11~D8 上,而低 8 位数据总线必须为双向输入输出,所以采用 2 个锁存器分别锁存读写 2 个方向的数据,而输出则通过三态门进行控制,以防止总线冲突。这样 TMS320LF2407A 可以通过对相关片外地址写不同

的数据来实现对 DS12C887 的不同控制功能, 按照相应的时序对该地址进行一系列访问来完成相应的操作。读写子程序代码如下。

$t_{L(COH - CNTL)}$  - 选通建立延迟时间;  $t_{h(D)W}$  - 数据保持时间;

$t_{d(COH - CNTL)}$  - 选通撤除延迟时间;  $t_{dS(W - D)}$  - 撤除时间;

$t_{d(COH - A)W}$  - 写地址有效延迟时间;  $t_{h(A)COLW}$  - 地址保持时间;

$t_{d(COH - RWL)}$  -  $R/\bar{W}$  写有效延迟时间;  $t_{su(A)W}$  - 地址建立时间;

$t_{d(COL - WL)}$  - 写使能延迟时间;  $t_{d(COL - WH)}$  - 写结束延迟时间;

$t_{er(D)COL}$  - 数据使能时间;  $t_{su(D)W}$  - 数据有效建立时间;

$t_{OL - SL}$  -  $\overline{STRB}$ 建立延迟时间;  $t_{d(COL - SH)}$  -  $\overline{STRB}$ 撤除延迟时间

$t_{d(COH - RWH)}$  -  $R/\bar{W}$  写撤除延迟时间;

图3 TMS320SLE345A片外数据存储器同时写入

$t_{su(D)RD}$ —读数据建立时间;  $t_{(RDY)COH}$ —READY 有效时间;

$t_{V(RDY)ARD}$ —READY 保持时间;  $t_{su(RDY)COH}$ —读数据建立时间

$t_{(RDY)ARD}$ —地址延迟空时间

图 4 TMS320LF2407A 片外数据存储器读时序

### 写一个字节数据子程序.

```

void wrtime( unsigned int a, unsigned int b)

{

_CS887= 0x0700| a;

_CS887= 0x0600| a;

_CS887= 0x0400| b;

_CS887= 0x0400| b;

_CS887= 0x0e00| b;

_CS887= 0x0f00| b;

asm(" nop");

}

```

## 读一个字节数据子程序·

```

unsigned int rdtim e( unsigned int a)

{

unsigned int b;

_CS887= 0x0700| a;

_CS887= 0x0600| a;

_CS887= 0x0200| a;

_CS887= 0x0e00| a;

_CS887= 0x0f00| a;

b= _CS887;

asm(" nop");

return(b);

}

```

TMS320LF2407A 与 DS12C887 的接口电路如图 5 所示, CPLD 内部接口电路原理如图 6 所示。

图 5 TMS320LF2407A 与 DS12C887 的接口电路

### 3 接口设计中应注意的问题

在上述接口设计过程中需要解决以下 4 个方面的匹配问题<sup>[5]</sup>。

### (1) 速度的匹配

TMS320LF2407A 是一款高速芯片, 其内部时钟为 40 MHz, 而 DS12C887 是慢速器件, 这里将 DS12C887 配置为 INTEL 工作模式。本文采用不同的数据线来模拟 DS12C887 控制线的方式, 虽然二者在速度上不匹配, 但是由于每条访问语句都是采用 C 语言编程, 在访问中还带有数据信号, 所以实际在对 DS12C887 访问前还有一个数据预处理的过程, 该过程在代码反汇编时也可以看到。该过程的处理时间足够使 DS12C887 完成上一步的动作执行, 故在相邻 2 条访问语句间无需插入等待指令。当然为了保证可靠性, 可以适当增加空操作来完成速度的匹配。

## (2) 信号电平的匹配

TMS320LF2407A 采用 3.3V 电源供电，所有

图 6 CPLD 内部接口电路原理

的逻辑电平都是基于 3.3 V 的 LVTTL, 但是 DS12C887 是为 51 系列单片机设计的, 其电平是与 51 系列单片机一致的基于 5 V 的 TTL 电平, 二者之间互联时存在电平匹配的问题, 而 EPM7128SLV84 CPLD 在其 VCCINT 管脚配置成 5 V 时支持 3.3 V 或 5 V I/O 操作, 但是要注意在配置时应将 EPM7128SLV84 的 VCCIO 管脚配置成 3.3 V, 这样使 I/O 管脚输出电平不至于高过 3.3 V, 以免损坏与之相连接的 TMS320LF2407A 芯片。

### (3) 信号格式的匹配

信号格式匹配问题的处理比较简单, 二者只在总线位数上有所差别。TMS320LF2407A 是 16 位数据与地址并行总线, 而 DS12C887 是 8 位数据与地址分时复用并行总线, 其它方面如电流量、电压

量、数字量、开关量上不存在不匹配问题, 所以只需在编写软件时进行一下处理, 在读时钟数据时 TMS320LF2407A 数据总线中的高 8 位忽略、写时钟数据时 TMS320LF2407A 数据总线的高 8 位中用到的 4 位配置成相应的数据、没有用到的位给任意数据即可。

### (4) 时序的匹配

时序匹配是本接口设计的关键, 由于相关的控制信号与数据信号同时发出, 这就要求先将数据信号锁存在锁存器中, 等待控制信号完成读写功能识别等相关功能后再开启相应的三态门完成本次操作。从时序图与相关的数据手册上可知, 在进行写操作时不需要插入延时, 但是在读操作时, 在控制信号作用到 DS12C887 后 20~120 ns 为 DS12C887 的反应时间, 经过这段反应时间后数据才会出现在总线上, 因此, 在读操作信号有效到锁存控制信号有效之间应插入一个有效延时, 可用 CPLD 时钟信号作为时基来对读有效信号进行 100 ns 的延时, 而 RD 信号的下降沿正好可以作为读有效信号, 这样就实现了二者时序上的匹配。

## 4 结语

介绍的采用 CPLD 实现的 TMS320LF2407A DSP 驱动 DS12C887 时钟芯片的电路已应用于某继电保护产品中, 应用效果良好, 未出现读写错误现象, 数据真实可靠, 是一种解决 2 种总线器件之间互连的可行方法。

## 参考文献:

- [1] 陆玉军, 吴英, 李澄. 用 DSP 实现时钟芯片 DS12C887 工作的一种方法 [EB/OL]. [2010-01-27]. <http://www.zgzn.com/article/Html/20095/1175.asp?temp=1175>.

- [2] 潘松, 黄继业. EDA 实用教程 TMS320LF240X DSP 原理及应用 [M]. 3 版. 北京: 科学出版社, 2006.

- [3] 周荷琴, 吴秀清. 微型计算机原理与接口技术 [M]. 4 版. 合肥: 中国科学技术大学出版社, 2008.

- [4] 菅睿, 李树华, 孙莉莉, 等. 基于 CPLD 芯片控制的日历时钟显示系统 [J]. 内蒙古大学学报, 2005, 36(4): 441-444.

- [5] 周遐, 金瑞, 钟思佳, 等. 基于 CPLD 和 DSP 的高速外部接口 [J]. 昆明冶金高等专科学校学报, 2009, 25(1): 32-36.