文章编号:1671-251X(2010)01-0127-03

# 基于 DDS 的数字调制器载波产生电路的设计

张楠<sup>1,2</sup>, 张根栋<sup>2</sup>

(1. 山西大同大学工学院, 山西 大同 037003; 2. 中国矿业大学信电学院, 江苏 徐州 221008)

**摘要:**从 DDS 基本原理出发,介绍了一种利用 FPGA 技术实现数字调制器载波产生电路的设计方案,给出了 FPGA 软件的关键程序设计。实验结果验证了该电路的可行性和有效性。

**关键词:**数字调制器; 载波信号; QPSK 调制; DDS; FPGA

**中图分类号:**TD655.2      **文献标识码:**B

## 0 引言

随着通信系统的数字化发展,数字信息的传输成为亟需解决的问题。结合传统的信号传输方式,

收稿日期:2009-09-07

作者简介:张楠(1981-),男,山西大同人,现为山西大同大学工学院教师,同时为中国矿业大学信电学院在读硕士研究生,研究方向为通信与信息系统。E-mail:zhangnan19810126@163.com

人们利用数字信号来控制正弦载波的某些参量,从而实现了数字信号的模拟传输<sup>[1]</sup>。但是在很多系统中仍然是使用模拟电路产生载波,利用专用芯片搭建电路来实现数字传输。参考文献[2]中提到的 QPSK 调制器就是完全使用独立的专用芯片来实现的。随着技术的进步,人们开始考虑摆脱专用集成芯片在体积和功耗等方面的限制,使用可编程逻辑器件来实现 QPSK 调制系统。参考文献[3]给出了一种基于可编程逻辑芯片的 QPSK 设计。在该设

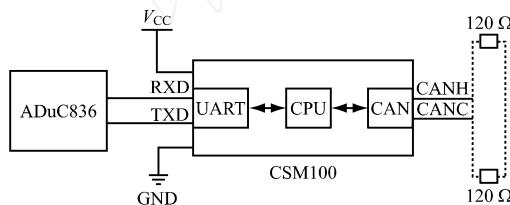

图 4 CSM100 的功能框图

## 2 压力变送器系统设计

由于 ADuC836 指令与 8051 兼容,故可以利用 8051 单片机的软件资源开发该压力变送器的软件程序;充分利用 ADuC836 提供的内部校准和系统校准功能,定时进行内部零位和满量程校准,解决了除传感器之外的漂移误差。

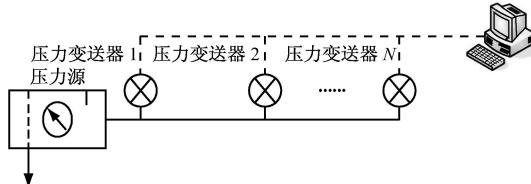

该压力变送器还具有非常方便的在线标定校准功能,如图 5 所示,同时将多只压力变送器连接同一个压力源,通过 CAN 总线与 PC 机相连,通过上位机软件可实现多只变送器同时标定校准。

上位机同时记录标准压力值和被校表对应的电压值,经过温度补偿后,再通过 CAN 总线将标定分别下载到压力变送器单片机的数据存储器中,完成标定工作。

图 5 数字压力变送器在线标定校准示意图

## 3 结语

本文设计的基于 CAN 总线传输的数字压力变送器具有精度高、体积小、集成度高、可靠性高、智能化、成本低等特点,并具有在线标定校准和温度补偿功能,可用于不同的工业场合。

### 参考文献:

- [1] 夏义全,牟志平.应变片压力传感器变送电路的设计[J].科技资讯,2007(32).

- [2] 饶运涛,邹继军,郑勇芸.现场总线 CAN 原理与应用技术[M].北京:航空航天大学出版社,2003.

- [3] 张燕,张海宁,任安虎.基于 ADuC834 数字传感器的设计[J].科技广场,2008(3).

- [4] 卜江春,孟思齐,蔡亮,等.基于 DSP 的真空断路器智能在线监测系统[J].工矿自动化,2008(3).

计中,串并转换部分和差分相位编码是在可编程逻辑芯片中实现的,这样就大大提高了系统的集成度和可靠性,但是其调制部分还是在模拟器件中实现的,并没有最大程度地实现数字化。本文采用先进的 DDS(Direct Digital Synthesizer,直接数字频率合成)技术,设计了一种以可编程逻辑芯片 FPGA 为主体的全数字 QPSK 调制器载波产生电路。在时钟信号的作用下,它可以产生频率可调的、任意相位的正弦波形,而且只要对其中的幅度码稍加改变,就几乎可以实现任意的周期波形,可以用作数字信号产生器,实现了原先只有在模拟域中才可以实现的 QPSK 调制,具有系统实现更加集成、可靠性更高的优点。

## 1 数字调制器载波产生电路设计原理

利用可编程逻辑器件产生全数字 QPSK 调制器的载波是指在数字器件中产生模拟信号。仅从字面上看这是不可能实现的事情。因为模拟信号的连续性在只有 0、1 两种状态的数字系统中是根本无法实现的,所以这里讲的只是在数字器件中实现载波的表示。利用这个“模拟载波的数字表示”对信号进行调制,最后利用 D/A 转换环节实现模拟信号的输出。

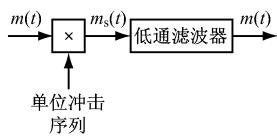

### 1.1 数字载波产生的理论依据

根据抽样定理:对某一带宽有限的连续时间信号即模拟信号进行抽样,如果抽样速率达到一定数值,就可以根据这些抽样值准确地恢复出原信号,如图 1 所示。其中  $m(t)$  为原始信号,它与周期冲击序列在时域相乘,得到均匀间隔的冲击序列,这些冲击的强度等于相应瞬时  $m(t)$  的值,它表示对原始信号  $m(t)$  的抽样。只要抽样点足够多,在还原端将该冲击序列通过低通滤波器即可恢复完整的原始信号。

图 1 抽样定理原理图

### 1.2 DDS 原理与计算

一个频谱纯净的单频信号可表示为

$$u(t) = U \sin(2\pi f_0 t + \phi_0) \quad (1)$$

只要幅度  $U$  和初始相位  $\phi_0$  不随时间变化,为常数,它的频谱就是位于  $f_0$  的一条谱线。为了简化分析,令  $U = 1$ ,  $\phi_0 = 0$ , 得到:

$$u(t) = \sin(2\pi f_0 t) = \sin(\omega_0 t) = \sin(\theta(t)) \quad (2)$$

这种单频信号的主要特性是它的相位是时间的线性函数,即:

$$\theta(t) = \omega_0 t = 2\pi f_0 t \quad (3)$$

相位函数对时间的导数是一常数:

$$\frac{d\theta(t)}{dt} = \omega_0 = 2\pi f_0 \quad (4)$$

也就是信号的频率。

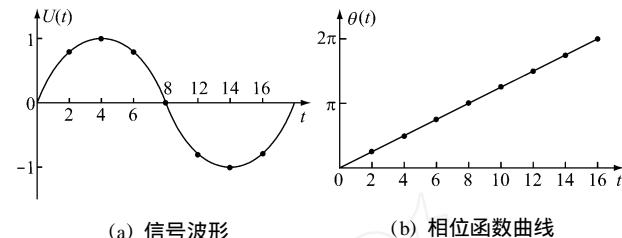

信号波形和相位函数曲线如图 2 所示。相位函数是一条直线,它的斜率就是信号的频率。

图 2 信号波形和相位函数曲线

如果对该单频信号采样,采样周期为  $T_c$ (即采样频率为  $f_0 = 1/T_c$ ),即可得到离散的波形序列:

$$u^*(n) = \sin(2\pi f_0 n T_c) \quad (5)$$

相应的离散相位序列为

$$\theta^*(n) = 2\pi f_0 n T_c = \dots \cdot n \quad (6)$$

式中: $n = 0, 1, 2, \dots$ ;  $\omega_0 = 2\pi f_0 = 2\pi f_0/T_c$ , 为连续 2 次采样之间的相位增量。

该离散相位序列和离散波形序列如图 2 中的黑点所示。如果采样值在间隔时间内保持不变,则相位和波形都将变成阶梯形。

### 1.3 硬件电路设计

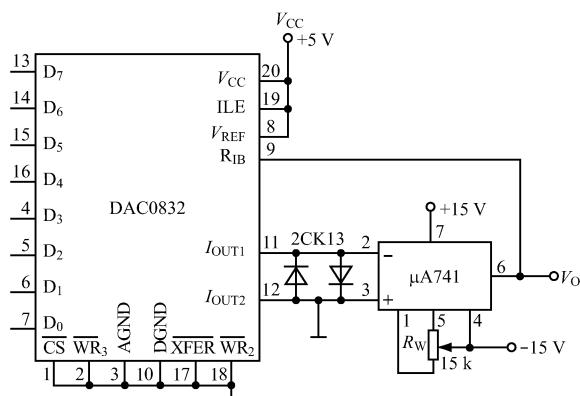

数字调制器载波产生电路的主要功能就是实现数字信号到模拟波形的转换。在该过程中最直接的方式就是使用专门的 D/A 转换芯片。笔者选用 DAC0832 芯片,它是采用 CMOS 工艺制成的单片电流输出型 8 位数/模转换器,核心部分采用倒 T 型电阻网络的 8 位 D/A 转换器<sup>[6~7]</sup>。DAC0832 的输出为电流信号,要转换为电压信号,还必须经过一个外接的运算放大器<sup>[8]</sup>,这样才能得到用于 QPSK 调制的正弦载波。数字调制器载波产生电路如图 3 所示。

## 2 数字调制器载波产生电路的程序设计

在本设计中,采用 VHDL 语言<sup>[9]</sup>直接对系统进行描述<sup>[10~11]</sup>。

在 DDS 的产生中,需要用统一的触发时钟来控制系统动作,通常利用时钟的 1 个上升沿来触发

图 3 数字调制器载波产生电路图

1 个动作。相关语句如下：

```

if clk'event and clk='1' then

.....

end if ;

```

相位累加的作用是使系统输出周期变化的相位码。在 VHDL 语言中利用这样的语句描述：

```

if reset = '1' then

temp := 0;

else

if (temp + k) > 199 then

temp := temp + k - 200;

else

temp := temp + k;

end if;

end if;

```

其中  $k$  为增量控制输入,也就是频率控制字;

$reset$  是用于复位的控制端;  $temp$  是存放相位码的

变量。在程序中使  $temp$  的值以  $k$  为增量进行递

加。本设计对正弦信号的 1 个周期进行 200 次采

样,所以只存在 200 种相位码。相位码变量  $temp$

的值一旦大于 200 就将其值减去 200,以免相位码

溢出。相位码到幅度码的转换可以使用 case 语句

实现,相关程序如下:

```

case temp is

when 0 = > qOUT < = "10000000";

when 1 = > qOUT < = "10000100";

.....

when 198 = > qOUT < = "01110111";

when 199 = > < = "01111011";

when others = > null;

end case;

```

其中  $q_{\text{OUT}}$  为载波产生电路的幅度码输出端。

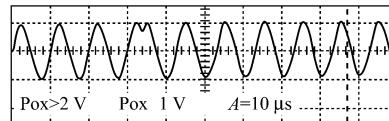

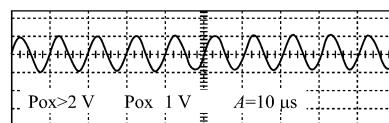

应用上述程序后输出的调制载波和已调波波形

如图 4、图 5 所示。从图 4、图 5 中看出，应用该设计方案是有效的。

图 4 全数字 QPSK 调制载波波形

图 5 已调波波形

3 结语

本文介绍的全数字 QPSK 调制器载波产生电路将 FPGA 和 EDA 技术的发展和优势应用到 QPSK 调制系统的设计中,完成了一个传统模拟调制系统的全新数字实现。该电路具有低功耗、低成本、高度集成的优点,具有很高的使用价值和一定的市场潜力。

## 参考文献：

- [ 1 ] 樊昌信,张甫翊,徐炳祥,等. 通信原理 [ M ]. 北京: 国防工业出版社,2003.

- [ 2 ] 董钧良. 移动通信和个人通信系统的数字调制技术 [ J ]. 电信快报,1995(11):11-16.

- [ 3 ] 郭道省,甘仲民,张邦宁,等. 数字卫星电视信号调制技术的研究 [ J ]. 电视技术,2001(5):49-51.

- [ 4 ] 孙学康,张 政. 微波与卫星通信 [ M ]. 北京:人民邮电出版社,2003.

- [ 5 ] 张厥盛,曹丽娜. 锁相与频率合成技术 [ M ]. 成都:电子科技大学出版社,1995.

- [ 6 ] 胡汉才. 单片机原理及其接口技术 [ M ]. 北京:清华大学出版社,2001.

- [ 7 ] 康华光,陈大钦. 电子技术基础模拟部分 [ M ]. 4 版. 北京:高等教育出版社,1999.

- [ 8 ] 曹国清. 数字电路与逻辑设计 [ M ]. 徐州:中国矿业大学出版社,1998.

- [ 9 ] 陈耀和. VHDL 语言设计技术 [ M ]. 北京:电子工业出版社,2004.

- [ 10 ] 姜志鹏. 基于 FPGA 的 2DPSK 信号产生器的设计与实现 [ J ]. 现代电子技术,2003(21):28-30.

- [ 11 ] 胡振华. VHDL 与 FPGA 设计 [ M ]. 北京:中国铁道出版社,2003.