文章编号:1671-251X(2009)02-0093-02

# 基于 VHDL 的 LCD 控制器的设计与实现

周雷,付慧生,熊建伟

(中国矿业大学信电学院,江苏徐州 221008)

**摘要:**文章介绍了基于 VHDL 语言状态机的 LCD 控制器的设计方法,说明了字符型液晶显示器显示的基本原理,给出了显示字符的方法及实现 LCD 控制器的部分 VHDL 语言程序。基于 VHDL 设计的 LCD 控制器具有很好的移植性,稍加改动就可以应用到不同场合。

**关键词:**LCD 控制器;VHDL;字符显示

**中图分类号:**TP312

**文献标识码:**B

## 0 引言

传统的 LCD 控制器通常由单片机组成,具有集成电路复杂、移植性差等缺点。随着可编程逻辑器件的发展,以 FPGA(现场可编程门阵列)为平台,采用硬件编程语言来实现 LCD 控制器,具有易于集成到片上系统、方便修改、适应不同液晶显示器等优点。

本文设计的 LCD 控制器是一种基于 FPGA 的液晶显示控制器,它采用 VHDL 语言实现控制器的编程设计,这种设计方法稍加改动就可以应用于常见的 LCD 接口电路中<sup>[1]</sup>。

## 1 CFAH1602B - TMC - JP 型液晶显示器

### 1.1 液晶显示器简介

LCD 是基于液晶电光效应的显示器件,利用液晶的物理特性,在通电时导通,使液晶排列变得有秩序,使光线容易通过;不通电时,排列则变得混乱,阻止光线通过。字符型液晶模块是一种用点阵图形来显示字符的液晶显示器,根据显示的容量可以分为 1 行 16 字、2 行 16 字、2 行 20 字等类型。本设计采

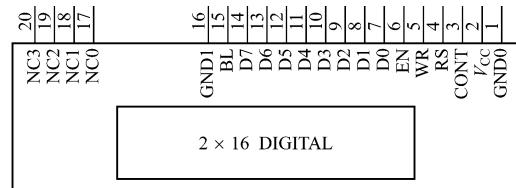

用 Crystalfontz 公司的 CFA H1602B - TMC - JP 型液晶显示器器件,它是 2 行 16 字的显示器件,可以显示 192 种 (5 × 7) 字符,32 种 (5 × 10) 字符,可自编 8 (5 × 7) 或 4 (5 × 10) 种字符。该显示器的工作电压为 5 V,其引脚如图 1 所示。

图 1 CFA H1602B - TMC - JP 显示器的引脚图

### 1.2 字符显示方法

液晶显示的字符可以通过控制引脚的改变来选择是外部数据输入还是取其内部储存的字符。CFA H 1602B - TMC - JP 型液晶显示器内部的字符发生存储器(CGROM)已储存了 192 种不同的点阵字符图形,这些字符包括英文字母、阿拉伯数字、常用的符号等。每一个字符都有其固定的代码,比如阿拉伯数字“1”的代码为 00110001B (31H),要显示数字“1”时可以直接从 CGROM 中读取,把数字“1”显示在液晶屏上。

由于 CFA H1602B - TMC - JP 型液晶显示器为 16 × 2 型显示,在显示字符时需要确定字符显示的地址,即字符显示在哪行哪列。比如第二行第一列的地址是 40H,当要在该地址显示字符时,

收稿日期:2008-10-29

作者简介:周雷(1985-),男,中国矿业大学信号与信息处理专业 2006 级硕士研究生,研究方向为 EDA 技术应用。E-mail:zhou135@163.com

### 参考文献:

- [1] 高丽珍.新型矿用本质安全型电源的设计与研究[J].机械工程与自动化,2006(3):125~127.

- [2] 杨智敏,侯传教,刘霞.单片式开关稳压器 LM2576

- ADJ 及其应用 [J]. 移动电源与车辆,2004(1):34~36.

[3] 张乃国.电源技术[M].北京:中国电力出版社,1998.

[4] 崔保春,王聪,卢其威,等.矿用本质安全开关电源的研究[J].中国煤炭,2006(3):49~51.

因为写入显示地址时要求最高位 D7 恒为高电平, 所以实际写入的地址应为 C0H。

FPGA 为 LCD 提供时序以及数据的控制,LCD 可根据 FPGA 的控制信号读取自身存储的字符或读取 FPGA 通过数据通道传送的数据信息并进行显示。

## 2 软件设计

VHDL 语言是一种面向设计、多层次的标准化硬件描述语言, 是描述、验证和设计数字系统的重要标准语言之一, 为设计者开辟了一种全新的数字系统的设计途径<sup>[2]</sup>。利用 VHDL 编写的电路模块代码可被重复利用, 可简化设计者的设计工作, 大大缩短设计时间, 提高工作效率。

本文设计的 LCD 控制器的软件模块主要包括初始化模块、写数据模块等, 都使用 VHDL 语言编写。

### 2.1 初始化模块

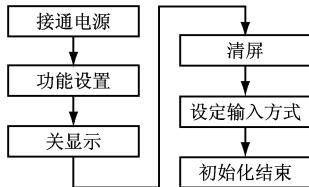

液晶在上电过程中, 开始必须进行初始化, 否则模块无法正常显示。初始化有 2 种方法: 一是利用内部复位电路进行初始化, 二是利用软件进行初始化。本文采用软件初始化方法。在整个初始化过程中, 数据都被送入指令寄存器中。所以, 必须保证 LCD 的引脚 RS 为低电平。笔者采用 VHDL 语言的状态机来实现液晶的初始化过程<sup>[3]</sup>。图 2 为初始化程序流程图。

图 2 初始话程序流程图

### 2.2 写数据模块

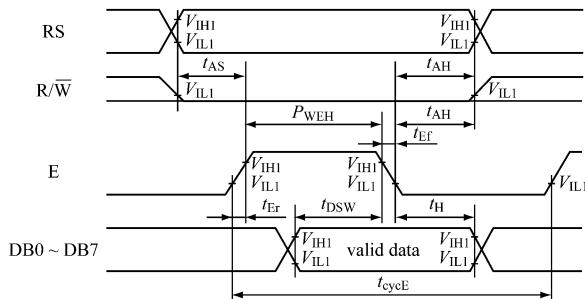

液晶初始化完成以后, 便可以写入数据。写入数据时, 首先应该选择数据寄存器, 其次是输入要写数据的地址, 最后再输入数据。由于数据是在 EN 的上升沿时刻输入, 但是在 EN 下降沿时刻才执行, 所以, 输完地址以后要确定 EN 为下降沿以后, 才能继续输入数据, 否则数据就会被冲掉。图 3 为数据写入的工作时序。

写数据也采用状态机来实现, 部分 VHDL 程序如下:

```

when Tshow0 = > --写操作时序 0

```

$V_{IH}$  - 输入高电压;  $V_{IL}$  - 输入低电压;  $t_{AS}$  - 地址建立时间;

$t_{AH}$  - 地址保持时间;  $P_{WEH}$  - 使能脉冲宽度;  $t_H$  - 使能上升/下降时间;

$t_{EF}$  - 使能上升/下降时间;  $t_{DSW}$  - 数据建立时间;

$t_H$  - 数据保持时间;  $t_{cycE}$  - 使能周期时间

图 3 写数据的工作时序图

```

lcdRS <= tempLcdRS;

lcdRW <= '0';

next_stateT <= Tshow1;

when Tshow1 = > -- 写操作时序 1

lcdRS <= tempLcdRS;

lcdRW <= '0';

lcdE <= '1';

next_stateT <= Tshow2;

when Tshow2 = > -- 写操作时序 2

lcdRS <= tempLcdRS;

lcdRW <= '0';

lcdE <= '0';

next_stateT <= Tshow3;

when Tshow3 = > -- 写操作时序 3

lcdRS <= '0';

lcdRW <= '1';

lcdE <= '0';

```

## 3 结语

本文设计的 LCD 控制器采用硬件描述语言 VHDL, 以 FPGA 为控制核心实现对字符点阵液晶显示器的控制, 具有简单、稳定、便于修改和移植、可重用性好的特点。该控制器已经在 ALTERA 公司的 DE2 板上实现其显示功能, 效果较好。本设计为嵌入式系统人机界面中的 LCD 控制驱动与接口设计提供了一种可靠而实用的设计方案。

## 参考文献:

- [1] 罗苑棠. CPLD/FPGA 常用模块与综合系统设计实例精讲 [M]. 北京:电子工业出版社, 2007.

- [2] 付慧生. 复杂可编程逻辑器件与应用设计 [M]. 徐州:中国矿业大学出版社, 2003.

- [3] 姜立东. VHDL 语言程序设计及应用 [M]. 北京:北京邮电大学出版社, 2001.